Fonctionnalités clés

- Prise en charge des tests de 400 MHz, 533 MHz, 667 MHz, 800 MHz, 1066 MHz et des niveaux de vitesse personnalisés des signaux DDR2

- Le moyen le plus rapide de gagner en confiance dans votre interface DDR2 en mesurant un grand nombre de cycles et en rapportant les résultats statistiques

- Capture d'écran de mesure du pire cas entièrement annotée capturée et affichée dans le rapport, y compris les étiquettes de trace et les niveaux de tension pertinents

- La capacité d'arrêt en cas de test/échec permet à l'utilisateur de faire une pause à un test particulier et de revoir la mesure sur l'écran de l'oscilloscope

- Couverture complète des tests pour les tests décrits dans les spécifications JESD79-2E et JESD208 JEDEC et Intel DDR2 667/800 JEDEC Specifications Addendum Rev. 1.1 et Intel DDR2 400/ 533 JEDEC Specifications Addendum Rev. 1.0

La solution de test Teledyne LeCroy QPHY-DDR2 est le meilleur moyen de caractériser les interfaces mémoire DDR2. Capable d'effectuer des mesures sur 400 MHz, 533 MHz, 667 MHz, 800 MHz, 1066 MHz et des niveaux de vitesse personnalisés, QPHY-DDR2 dispose d'une suite complète de tests d'horloge, électriques et de synchronisation, comme spécifié par la spécification JEDEC et les addendums aux spécifications Intel JEDEC.

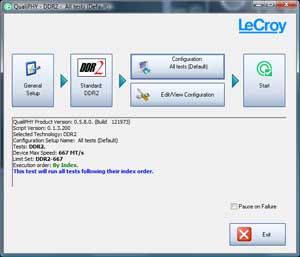

La plate-forme Teledyne LeCroy QualiPHY fournit une interface utilisateur facile à configurer, permet des tests personnalisés et une sélection de limites, affiche des schémas de connexion à l'utilisateur pour assurer une connectivité appropriée et génère des rapports avec tous les résultats, y compris des captures d'écran des pires cas de défaillance pour chaque cas applicable. test. De plus, toutes les formes d'onde testées par QPHY-DDR2 peuvent être enregistrées pour partager facilement des informations ou réexécuter les tests ultérieurement.

QPHY-DDR2 permet à l'utilisateur d'obtenir le plus haut niveau de confiance dans son interface DDR2. En raison du niveau élevé de variabilité des mesures DDR2, il est important de mesurer un grand nombre de cycles. En mesurant un grand nombre de cycles dans un laps de temps très court, l'utilisateur peut être plus sûr qu'il attrape les vrais points maximum et minimum pour sa mesure.

En plus de la caractérisation automatisée des signaux DDR2, QPHY-DDR2 permet également une puissante capacité de débogage pour les signaux DDR2 à l'intérieur de l'oscilloscope. Les causes profondes des défaillances peuvent être trouvées rapidement et facilement à l'aide de tous les outils de données série avancés de l'oscilloscope. Ceux-ci incluent : SDA II, Eye Doctor™ II, WaveScan™ et bien d'autres.

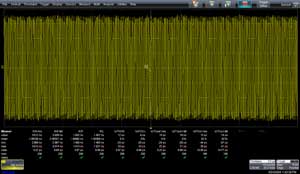

Tests d'horloge - Ces tests effectuent tous les tests d'horloge comme décrit par la spécification JEDEC appropriée. Ceux-ci incluent la période d'horloge moyenne, la période d'horloge absolue, la largeur d'impulsion haute/basse moyenne, la largeur d'impulsion haute/basse absolue, la gigue de demi-période, la gigue de période d'horloge, la gigue de période cycle à cycle et l'erreur cumulée sur n tests de période.

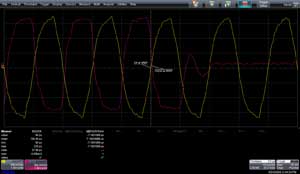

Tests électriques – Ces tests mesurent les caractéristiques électriques des signaux DDR2. Illustré ci-dessus, le test SoutR mesure les vitesses de balayage des signaux de données, d'échantillonnage et d'horloge. Plus de 1000 mesures de vitesse de balayage ont été effectuées et la pire instance a été affichée à l'écran. Les signaux sont annotés avec les noms des signaux pour faciliter l'interprétation de l'écran. De plus, des curseurs sont utilisés pour montrer à l'utilisateur les niveaux de tension entre lesquels la vitesse de balayage a été mesurée.

Test de synchronisation - Ces tests vérifient la relation temporelle entre des événements DDR2 particuliers. Illustré ci-dessus, le test tDQSCK vérifie que le temps d'accès à la sortie d'échantillonnage à partir du signal d'horloge est dans la limite spécifiée par la spécification JEDEC appropriée. Dans ce test, 5000 mesures tDQSCK ont été effectuées sur toutes les rafales de lecture DDR2 et la pire instance a été affichée à l'écran.

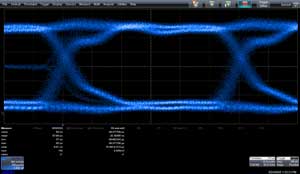

Diagrammes de l'œil – Les diagrammes de l'œil sont un outil puissant pour le débogage des signaux de données série. QPHY-DDR2 permet à l'utilisateur de créer des diagrammes en œil des rafales de données de lecture et d'écriture pour s'assurer que l'intégrité du signal est suffisante pour que les données soient échantillonnées correctement par le récepteur.

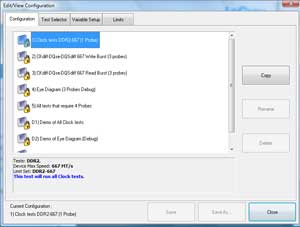

QualiPHY possède de nombreuses configurations de conformité prédéfinies, mais permet également aux utilisateurs de créer leurs propres configurations et ensembles de limites.

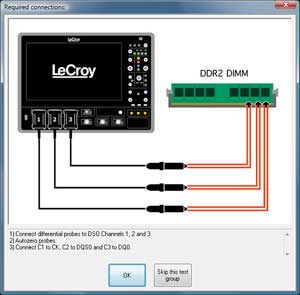

Les schémas de connexion invitent l'utilisateur à effectuer les connexions nécessaires.

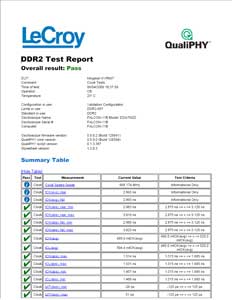

Les rapports de conformité contiennent toutes les valeurs testées, les limites de test spécifiques et les captures d'écran. Les rapports de conformité peuvent être créés au format HTML, PDF ou XML.

QualiPHY

QualiPHY est conçu pour réduire le temps, les efforts et les connaissances spécialisées nécessaires pour effectuer des tests de conformité sur des bus série à haut débit.

- Guide l'utilisateur à travers chaque configuration de test

- Effectue chaque mesure conformément à la procédure de test pertinente

- Compare chaque valeur mesurée avec les limites de spécification applicables

- Documente entièrement tous les résultats

- QualiPHY aide l'utilisateur à effectuer les tests de la bonne manière, à chaque fois !

Spécifications

Tests d'horloge

tCK(avg) – Période d'horloge moyenne

tCH(avg) – Largeur moyenne d'impulsion élevée

tCL(avg) – Largeur d'impulsion faible moyenne

tCK (abs) – Période d'horloge absolue

tCH(abs) – Largeur d'impulsion élevée absolue

tCL(abs) – Largeur d'impulsion basse absolue

tJIT(duty) – Gigue de demi-période

tJIT(per) – Gigue de la période d'horloge

tJIT(cc) – Gigue de période de cycle à cycle

tERR(n par) – Erreur cumulée

Débogage avancé

Diagramme de l'œil des données et du stroboscope sur le cycle de lecture

Diagramme de l'œil des données et du stroboscope sur le cycle d'écriture

Tests électriques

SlewR - Taux de balayage du front montant d'entrée

SlewF - Taux de balayage du front descendant d'entrée

VIH(ac) – Logique d'entrée CA haute

VIH(dc) – Logique d'entrée CC haute

VIL(ac) – Logique d'entrée CA faible

VIL(dc) – Niveau logique d'entrée CC bas

VSWING - Signal d'entrée maximal

Balançoire de crête à crête

SoutR - Augmentation de la vitesse de balayage de sortie

SoutF - Chute de la vitesse de balayage de sortie

tSLMR - Rapport d'adaptation de la vitesse de balayage de sortie

Amplitude de crête de dépassement CA

Zone de dépassement CA au-dessus de VDDQ

Amplitude maximale de sous-dépassement CA

Zone de sous-dépassement CA sous VSSQ

VID(ac) - Tension d'entrée différentielle CA

VIX (ac) - Tension de point de croisement d'entrée différentielle CA

VOX(ac) - Tension de point de croisement de sortie différentielle CA

Essais de chronométrage

tHZ(DQ) – Temps de haute impédance DQ à partir de CK/CK#

tLZ(DQ) – Temps de faible impédance DQ à partir de CK/CK#

tLZ(DQS) – Temps de faible impédance DQS à partir de CK/CK#

tHP - CK demi-largeur d'impulsion

tQHS - Facteur d'inclinaison de maintien DQ

tQH – Temps de maintien de la sortie DQ/DQS à partir de DQS

tDQSH - Largeur d'impulsion élevée d'entrée DQS

tDQSL – Largeur d'impulsion faible d'entrée DQS

tDSS - Temps de configuration du front descendant DQS vers CK

tDSH - Temps de maintien du front descendant DQS à partir de CK

tWPRE - Écrire le préambule

tWPST - Écrire le postambule

tRPRE - Lire le préambule

tRPST - Lire le postambule

tDQSQ - Décalage entre DQS et DQ

tDQSS - Transition de verrouillage DQS vers le front d'horloge

tDQSCK – Temps d'accès à la sortie DQS à partir de CK/CK#

tAC – Temps d'accès à la sortie DQ à partir de CK/CK#

tDS(base) – Temps de configuration des entrées DQ et DM

tDH(base) – Temps de maintien des entrées DQ et DM

tIS(base) – Temps de configuration de l'adresse et de l'entrée de contrôle

tIH(base) – Temps de maintien de l'adresse et de l'entrée de contrôle

tDS1(base) – Temps de configuration des entrées DQ et DM (Strobe asymétrique)

tDH1(base) – Temps de maintien des entrées DQ et DM (Strobe asymétrique)